Cyber Secure and Resilient System-on-Chip

Cyber Secure and Resilient System-on-Chip using FPGA Dynamic Configuration, Post-Quantum Cryptography, AI/ML/LLM Accelerators

Overview

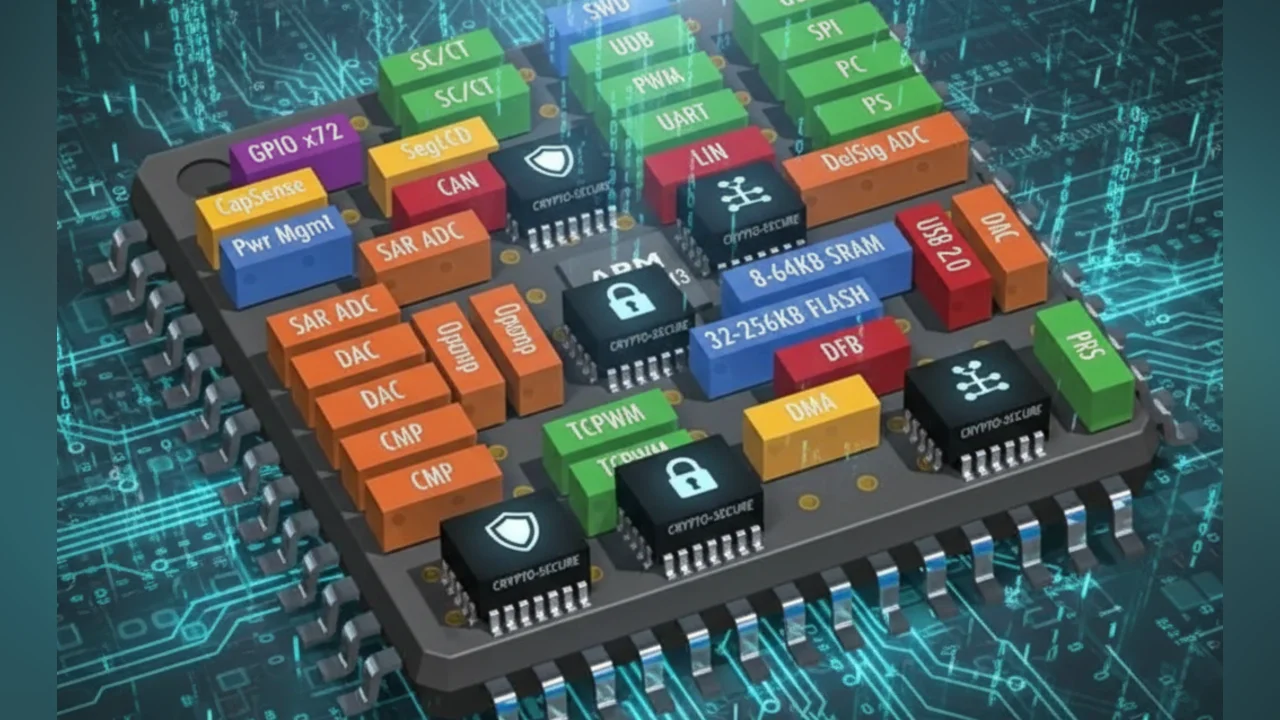

The genuine immutability properties of hardware components and elements make them ideal for security hardening and containment, i.e., by making the hard-implemented logic tamper-resistant against both benign and intrusion faults. Despite these facts, there is a continuous wave of relaxing these “rigid” hardware designs through introducing programmable (including reconfigurable and adaptable) fabric. The main reason is to improve hardware flexibility and compatibility, i.e., making them application-agnostic, and to facilitate the daunting design verification process prior to fabrication, hence cutting off fabrication costs thereof. For this, programmable hardware is considered a tradeoff between software logic— fully flexible, slow, and mutable—and hard logic—fully rigid, fast, and immutable. We believe that there are promising opportunities to boost the resilience of the programmable platforms against faults and intrusions, although immutability is slightly reduced [SoC].

This project explores the techniques to use FPGA dynamic reconfiguration to boost the resilience of a System-on-Chip [Samsara]. This can be done through changing the FPGA infrastructure itself, e.g., elastic dynamic partitioning, dimorph sizes and shapes, replicate partitions, etc.; or through changing the IP logic running on, e.g., dynamic Byzantine intrusion resilience protocols [Samsara], adaptive ML detection protocols, or loading different IPs as a threat response.

[SoC] Shoker, Ali, Paulo Esteves-Verissimo, and Marcus Völp. "The path to fault-and intrusion-resilient manycore systems on a chip." 2023 53rd Annual IEEE/IFIP International Conference on Dependable Systems and Networks-Supplemental Volume (DSN-S). IEEE, 2023.

[Samsara] Pinto Gouveia, Inês, et al. "Resilient and Secure Programmable System-on-Chip Accelerator Offload." arXiv e-prints (2024): arXiv-2406.